# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) Int. Cl.

HO1L 33/14 (2010.01) HO1L 33/06 (2010.01)

(21) 출원번호

10-2008-0071299

(22) 출원일자

2008년07월22일

심사청구일자 없음

101L 33/00 (2010.01)

(71) 출원인

(11) 공개번호

(43) 공개일자

삼성전기주식회사

경기도 수원시 영통구 매탄동 314

광주과학기술원

광주 북구 오룡동 1번지

(72) 발명자

강상원

경기 수원시 영통구 영통동 벽적골9단지아파트 936동 601호

10-2010-0010364

2010년02월01일

박성주

광주 북구 오룡동 광주과학기술원 신소재공학과 909호

(뒷면에 계속)

(74) 대리인

특허법인 씨엔에스·로고스

전체 청구항 수 : 총 18 항

# (54) 질화물 반도체 발광소자

#### (57) 요 약

본 발명은 다중 양자 우물 구조의 활성층을 구비한 질화물 반도체 발광 소자에 관한 것으로, 기판상에 버퍼층, n 형 질화물 반도체층, 활성층 및 p형 질화물 반도체층이 순차 적층된 질화물 반도체 발광소자에 있어서, 상기 활성층은 복수개의 장벽층과 복수개의 우물층이 교대로 배열된 다중 양자 우물(Multi Quantum Well) 구조를 가지며, 상기 복수개의 장벽층 중 적어도 1개 층은 p형 도펀트가 도핑된 p형 도핑 장벽층과 상기 p형 GaN층의 적어도 일측에 언도프된 장벽층을 갖는 제1 장벽층을 구비한다.

# 대 표 도 - 도3

# (72) 발명자

# 권민기

전라북도 전주시 완산구 효자동1가 상산타운 비사 벌아파트 102동 1101호

#### 이상준

광주광역시 북구 오룡동 광주과학기술원 신소재 공 학과

# 조주영

광주광역시 북구 오룡동 광주과학기술원 신소재 공 학과

# 김용천

경기 성남시 분당구 정자동 한솔마을한일아파트 301동 1802호

# 한상헌

경기도 수원시 영통구 매탄3동 314 삼성 LED

# 이동주

경기 수원시 영통구 매탄4동 동남아파트 2동 1012 호

#### 오정탁

경기 용인시 기흥구 영덕동 태영데시앙아파트 201 동 304호

# 김제원

서울 서초구 우면동 동양고속아파트 103동 1301호

#### 특허청구의 범위

#### 청구항 1

기판상에 적어도 버퍼층, n형 질화물 반도체층, 활성층 및 p형 질화물 반도체층을 순차 적층된 질화물 반도체 발광소자에 있어서,

상기 활성층은 복수개의 장벽층과 복수개의 우물층이 교대로 배열된 다중 양자 우물(Multi Quantum Well) 구조이며,

상기 복수개의 장벽층 중 적어도 1개 층은 p형 도펀트가 도핑된 p형 도핑 장벽층과 언도프된 장벽층을 갖는 제1 장벽층인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 2

제1항에 있어서.

상기 제1 장벽층은 상기 p형 질화물 반도체층에 인접한 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 3

제1항에 있어서,

상기 복수개의 장벽층 전체가 상기 제1 장벽층인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 4

제1항에 있어서.

상기 제1 장벽층은 p형 도펀트가 도핑된 질화물 반도체로 된 p형 도핑 장벽층 및 언도프된 질화물 반도체로 된 언도프된 장벽층이 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

## 청구항 5

제1항에 있어서,

상기 제1 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층 및 p형 도펀트가 도핑된 질화물 반도체로 된 p형 도핑 장벽층이 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 6

제5항에 있어서,

상기 제1 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층을 상기 p형 도핑 장벽층 상에 더 구비하여 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 7

제1항에 있어서.

상기 p형 도펀트는 Mg, Zn, Be, Ca, Sr 및 Ba 중 어느 하나인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 8

제1항에 있어서,

상기 p형 도펀트의 도핑 농도는  $10^{15}/cm^2 \sim 10^{20}/cm^2$  인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 9

제1항에 있어서,

상기 p형 도핑 장벽층의 도핑농도를 경사지게 하거나 계단식으로 성장시키는 것을 특징으로 하는 질화물 반도체

발광소자.

#### 청구항 10

제1항에 있어서.

상기 활성층은 상기 n형 질화물 반도체층에 인접한 영역에 n형 도펀트가 도핑된 복수개의 제2 장벽층을 더 구비하는 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 11

제10항에 있어서,

상기 제2 장벽층의 단일층은 n형 도펀트가 도핑된 n형 도핑 장벽층 및 언도프된 장벽층을 가지는 것을 특징으로 하는 질화물 반도체 발광소자.

# 청구항 12

제11항에 있어서,

상기 제2 장벽층의 단일층은 n형 도펀트가 도핑된 질화물 반도체로 된 n형 도핑 장벽층 및 언도프된 질화물 반도체로 된 언도프된 장벽층이 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 13

제11에 있어서,

상기 제2 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층 및 n형 도펀트가 도핑된 질화물 반도체로 된 n형 도핑 장벽층이 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 14

제13항에 있어서,

상기 제2 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층 을 상기 n형 도핑 장벽층 상에 더구비하여 순차 적층되어 있는 것을 특징으로 하는 질화물 반도체 발광소자.

# 청구항 15

제10항에 있어서,

상기 n형 도펀트는 Si, Ge, Se, Te 및 C 중 적어도 어느 하나인 것을 특징으로 하는 질화물 반도체 발광소자.

# 청구항 16

제15항에 있어서,

상기 p형 도펀트는 Mg, Zn, Be, Ca, Sr 및 Ba 중 어느 하나인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 17

제10항에 있어서.

상기 n형 도펀트의 도핑 농도는  $10^{15}/\mathrm{cm}^{20}/\mathrm{cm}^{20}$ 인 것을 특징으로 하는 질화물 반도체 발광소자.

#### 청구항 18

제17항에 있어서,

상기 p형 도펀트의 도핑 농도는  $10^{15}/cm^2 \sim 10^{20}/cm^2$  인 것을 특징으로 하는 질화물 반도체 발광소자.

# 명 세 서

# 발명의 상세한 설명

# 기술분야

[0001] 본 발명은 다중 양자 우물 구조의 활성층을 구비한 질화물 반도체 발광소자에 관한 것으로, 더욱 상세하게는, p 형 질화물 반도체층의 인접 장벽층에 Mg 도핑하여 p형 도핑 장벽층으로 변화시킴으로써 전자의 오버플로우 (overflow)를 방지하고, 정공 주입 효율을 개선하여 외부 양자 효율을 증가시킬 수 있는 다중 양자 우물 구조의 활성층을 구비한 질화물 반도체 발광 소자에 관한 것이다.

# 배경기술

- [0002] 최근, 질화물 반도체 발광소자의 개발이 진행되면서 휴대폰 키패드, 사이드뷰(Side View)용 광원뿐만 아니라 일 반적인 조명용 및 자동차의 전조등으로까지 그 응용 범위를 넓히고 있다.

- [0003] 휴대폰용으로 사용되는 LED의 경우, 20 mA의 동작 전류를 사용하게 되지만, 조명용 및 자동차의 전조 등에 사용되는 LED는 일반적으로 수백 mA의 동작 전류가 주입된다. 수백 mA의 전류를 주입함에 따라 기존의 저전류에서는 관찰할 수 없던 문제점이 나타나게 되는데 대표적인 것이 바로 "이피션시 드룹(Efficiency Droop)" 현상이다.

- [0004] 일반적으로 LED의 효율은 외부 양자 효율로 나타내며, 이는 내부 양자 효율에 광자 추출 효율의 곱이다. 이러한 외부 양자 효율이 동작 전류가 증가함에 따라 감소하는 현상을 "이피션시 드룹(Efficiency Droop)" 이라고 한다.

- [0005] 기존 다중 양자 우물 구조의 LED의 경우, "이피션시 드룹(Efficiency Droop)"이 약 10 A/c㎡의 전류밀도에서 나타나게 된다. 즉, 10 A/c㎡의 전류밀도보다 큰 동작 전류에서는 외부 양자 효율이 점점 감소하게 된다. LED 칩의 면적에 따라 전류밀도는 달라지겠지만 10 A/c㎡ 정도의 전류밀도를 동작 전류로 환산하면 20 mA 근처가 된다.

- [0006] 즉, 휴대폰용으로 사용하는 LED의 경우, 20 mA 이상의 전류에서는 동작 전류가 올라갈수록 LED의 효율 측면에서는 그 효율이 떨어지는 문제가 발생한다. 따라서 상기와 같은 "이피션시 드룹(Efficiency Droop)" 현상은 고전류 밀도를 필요로 하는 조명용 및 자동차의 전조 등에 LED를 사용하기 위해 반드시 해결해야 할 문제이다.

- [0007] 구체적으로, 기존 다중 양자 우물 구조의 활성층을 가지는 LED의 경우, 활성층은 발광이 일어나는 우물층인 InGaN층과 장벽층인 GaN층으로 구성된다. 우물층의 경우, 일반적으로 언도프층(undope layer)을 사용하게 되며, 장벽층의 경우 언도프층 내지는 Si 도핑을 통해 n-GaN층으로 사용한다.

- [0008] 장벽층에 Si 도핑을 하는 이유는 Si도핑을 통하여 우물층과 장벽층간의 계면 특성을 좋게 할 뿐만 아니라, 저항을 낮춤으로써 순방향 전압에서의 동작 전압을 낮추는 효과를 볼 수 있다. 또한, Si 도핑을 통하여 전자의 농도를 높임으로써 우물층인 InGaN층과 장벽층인 GaN층 사이의 격자 상수 차이로 인해 발생하는 스트레스(stress)로 인한 압전 필드(piezoelectric field)를 차단(screening)해 주는 효과를 얻는다.

- [0009] 이를 통하여 동작 전류가 증가함에 따라 발생하게 되는 청색 천이(blue-shift) 현상 또한 감소되며, 차단 (screening) 효과를 통하여 압전 필드에 의한 밴드 휨(band bending) 현상을 감소시켜 전자와 홀간의 파동 함수 의 중첩을 증가시켜 내부 양자 효율이 증가 된다.

- [0010] 이러한 방법은 주로 저전류 밀도에서의 LED 효율을 증가시키기 위한 방법으로 사용되어 왔다. 그러나 조명용 및 자동차의 전조 등과 같은 고전류 밀도를 요구하는 경우에 발생하는 "이피션시 드룹(Efficiency Droop)" 현상을 해결하지는 못한다.

- [0011] 또한, 일반적으로 정공이 전자에 비하여 이동도가 낮기 때문에 LED의 활성층으로 주입되는 효율이 낮게 된다. 반대로 전자는 유효질량이 가벼워서 이동도가 커서 활성층으로 잘 주입되게 된다.

- [0012] 따라서 정공은 주입이 잘되지 않는 반면 주입이 잘 되는 전자는 활성층을 지나 p형 질화물 반도체층 영역으로 넘어가게 된다. 이러한 현상은 고전류 밀도, 즉, 전기적으로 주입되는 캐리어의 농도가 높아질수록 심해지게 되고, 이러한 현상에 의하여 고전류 밀도로 갈수록 외부 양자 효율이 감소하게 된다.

- [0013] 이러한 현상을 개선하기 위해서 밴드갭이 큰 AlGaN으로 된 전자 장벽층(Electron Blocking Layer)을 활성층 상에 적층하는 경우도 있다. 이 역시 격자상수 차이에 의해 발생하는 압전 필드에 의하여 장벽의 역할을 제대로할 수 없어서 전자의 오버플로우(overflow) 현상을 막기가 어렵다.

- [0014] 상술한 바와 같이, 기존 다중 양자 우물 구조의 활성층을 갖는 LED는 저전류 밀도에서 고전류 밀도로 갈수록 정

공의 낮은 주입 효율과, 고전류 밀도에서의 높은 캐리어(carrier) 농도에 따른 비발광 오제(Auger) 결합에 의하여 외부 양자 효율이 감소하는 문제점이 있다.

# 발명의 내용

# 해결 하고자하는 과제

- [0015] 따라서, 본 발명에서는 장벽층에 Mg 도핑 하여 장벽층의 전자 구속 효과를 증가시키는 동시에, 발광이 일어나는 우물층에 정공을 효과적으로 주입할 수 있는 질화물 반도체 발광소자를 제공하고자 한다.

- [0016] 또한, 본 발명에서는 Mg 도핑된 장벽층의 전후에 언도프된 장벽층을 형성함으로써 장벽층에 도핑된 Mg의 확산을 방지할 수 있는 질화물 반도체 발광소자를 제공하고자 한다.

#### 과제 해결수단

- [0017] 본 발명에 따른 질화물 반도체 발광소자는, 기판상에 적어도 버퍼층, n형 질화물 반도체층, 활성층 및 p형 질화물 반도체층을 순차 적충된 질화물 반도체 발광소자에 있어서, 상기 활성층은 복수개의 장벽층과 복수개의 우물 층이 교대로 배열된 다중 양자 우물(Multi Quantum Well) 구조이며, 상기 복수개의 장벽층 중 적어도 1개 층은 p형 도펀트가 도핑된 p형 도핑 장벽층과 언도프된 장벽층을 갖는 제1 장벽층인 것을 특징으로 한다.

- [0018] 바람직하게는, 상기 제1 장벽층은 상기 p형 질화물 반도체층에 인접한 것을 특징으로 한다.

- [0019] 바람직하게는, 상기 복수개의 장벽층 전체가 상기 제1 장벽층인 것을 특징으로 한다.

- [0020] 바람직하게는, 상기 제1 장벽층은 p형 도펀트가 도핑된 질화물 반도체로 된 p형 도핑 장벽층 및 언도프된 질화물 반도체로 된 언도프된 장벽층이 순차 적층되어 있거나, 언도프된 질화물 반도체로 된 언도프된 장벽층 및 p 형 도펀트가 도핑된 질화물 반도체로 된 p형 도핑 장벽층이 순차 적층되어 있는 것을 특징으로 한다.

- [0021] 바람직하게는, 상기 제1 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층, p형 도펀트가 도핑된 질화물 반도체로 된 p형 도핑 장벽층 및 언도프된 질화물 반도체로 된 언도프된 장벽층이 순차 적충되어 있는 것을 특징으로 한다.

- [0022] 바람직하게는, 상기 p형 도펀트는 Mg, Zn, Be, Ca, Sr 및 Ba 중 어느 하나이며, 상기 p형 도펀트의 도핑 농도는  $10^{15}/\mathrm{cm} \sim 10^{20}/\mathrm{cm}$  이고, 상기 p형 도핑 장벽층의 도핑농도를 경사지게 하거나 계단식으로 성장시키는 것을 특징으로 한다.

- [0023] 한편, 상기 활성층은 상기 n형 질화물 반도체층에 인접한 영역에 n형 도펀트가 도핑된 복수개의 제2 장벽층을 더 구비하는 것을 특징으로 한다.

- [0024] 바람직하게는, 상기 제2 장벽층의 단일층은 n형 도편트가 도핑된 n형 도핑 장벽층 및 언도프된 장벽층을 가지는 것을 특징으로 한다.

- [0025] 바람직하게는, 상기 제2 장벽층의 단일층은 n형 도펀트가 도핑된 질화물 반도체로 된 n형 도핑 장벽층 및 언도 프된 질화물 반도체로 된 언도프된 장벽층이 순차 적층되어 있거나, 상기 제2 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층 및 n형 도펀트가 도핑된 질화물 반도체로 된 n형 도핑 장벽층이 순차 적층되어 있는 것을 특징으로 한다.

- [0026] 바람직하게는, 상기 제2 장벽층의 단일층은 언도프된 질화물 반도체로 된 언도프된 장벽층, n형 도펀트가 도핑된 질화물 반도체로 된 n형 도핑 장벽층 및 언도프된 질화물 반도체로 된 언도프된 장벽층이 순차 적층되어 있는 것을 특징으로 한다.

- [0027] 바람직하게는, 상기 n형 도펀트는 Si, Ge, Se, Te 및 C 중 적어도 어느 하나이며, 상기 p형 도펀트는 Mg, Zn, Be, Ca, Sr 및 Ba 중 어느 하나인 것을 특징으로 한다.

- [0028] 바람직하게는, 상기 n형 또는 p형 도펀트의 도핑 농도는  $10^{15}/cm^2 \sim 10^{20}/cm^2$  인 것을 특징으로 한다.

## 直 과

[0029] 본 발명에 따르면, 장벽층에 p형 도펀트의 도핑에 의해 밴드갭이 변화되어 우물층의 전자 구속력 및 우물층으로 의 정공 주입 효율을 개선시킴으로써 고전류 밀도에서의 LED의 외부 양자 효율의 감소를 개선시키는 효과가 있

다.

[0030] 또한, 본 발명에 따르면, 장벽층에 도핑되는 p형 도펀트의 농도를 조절하여 장벽층에서의 캐리어(carrier) 농도를 감소시켜 비발광 오제 결합을 감소시킴으로써 고전류 밀도에서의 LED의 외부 양자 효율의 감소를 개선시키는 효과가 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0031] 이하, 첨부된 도면을 참조하면서 본 발명에 따른 질화물 반도체 발광소자 및 그 제조방법의 바람직한 실시 형태를 상세히 설명한다.

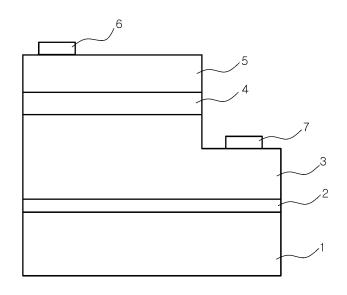

- [0032] 도 1은 본 발명의 바람직한 한 실시 형태인 질화물 반도체 발광소자의 구조를 나타낸 단면도이다.

- [0033] 도 1과 같이 질화물 반도체 발광소자는, 기판(1)상에 버퍼(buffer)층(2), n 형 질화물 반도체층(3), 다중 양자 우물 구조의 활성층(4), p형 질화물 반도체층(5)을 적충하고, 상기 n형 질화물 반도체층(3) 및 p형 질화물 반도 체층(5) 상에 각각 전극(6, 7)을 형성하여 반도체층(3, 5)으로부터 주입되는 정공과 전자의 재결합에 의해 활성 층(4)에서 광을 발생시킨다. 이때, 활성층(4)에서 발생된 광은 p형 질화물 반도체층(5)을 향하여 방출된다.

- [0034] 도 1에 도시된 질화물 반도체 발광소자의 각 구성요소에 대해 보다 상세하게 설명하면 다음과 같다.

- [0035] 기판(1)은, 그 위에 성장되는 질화물 반도체 물질과의 격자정합을 고려하여 사파이어 기판이 주로 사용된다. 이러한 사파이어 기판은 비교적 질화물 반도체 물질의 성장이 용이하며, 고온에서 안정하여 주로 사용된다.

- [0036] 기판(1)의 상면에 형성된 n형 질화물 반도체층(3)은 n형 도펀트로 도핑된 반도체 물질로 이루어질 수 있으며, 대표적인 질화물 반도체 물질로는 GaN, AlGaN, InGaN가 있다. 상기 n형 질화물 반도체층(3)의 도핑에 사용되는 도펀트로는 Si, Ge, Se, Te 또는 C 등이 사용될 수 있으며, 바람직하게는 Si를 사용한다.

- [0037] 상기 n형 질화물 반도체층(3)은, 상기 반도체 물질을 유기금속 기상증착법(Metal Organic Chemical Vapor Deposition : MOCVD), 분자빔 성장법(Molecular Beam Epitaxy : MBE) 또는 하이브리드 기상증착법(Hybrid Vapor Phase Epitaxy : HVPE)과 같은 공지의 증착공정을 사용하여 기판(1) 상에 성장시킴으로써 형성된다.

- [0038] 일반적으로, 기판(1)과 n형 질화물 반도체충(3) 사이에는 격자부정합을 완화하기 위한 버퍼충(2)이 형성될 수 있다. 이 버퍼충(2)으로는 통상 수십 mm의 두께를 갖는 GaN 또는 AlN 등의 저온핵성장층이 사용된다.

- [0039] 활성층(4)은 빛을 발광하기 위한 층으로서, 통상 InGaN층을 우물층로 하고, GaN층을 장벽층(barrier layer)으로 성장시켜 다중 양자 우물 구조(MQW)를 형성함으로써 이루어진다. 예를 들어, 청색 발광다이오드에서는 InGaN/GaN 등의 다중 양자 우물 구조, 자외선 발광다이오드에서는 GaN/AlGaN, InAlGaN/InAlGaN 및 InGaN/AlGaN 등의 다중 양자 우물 구조가 사용되고 있다. 상세한 설명은 도 2의 (b)에서 상세히 설명한다.

- [0040] 활성층(4)의 막두께는 특별히 한정되지 않고, LED 소자 등의 원하는 파장 등을 고려하여 우물층 및 장벽층의 적 층 수 또는 적층순서를 조정하여 활성층의 총막두께를 조정한다. 즉, In 또는 Al의 조성비율을 변화시킴으로써 빛의 파장을 조절하거나, 활성층 내의 양자 우물층의 깊이, 활성층의 수, 두께 등을 변화시킴으로써 발광다이오 드의 내부 양자 효율을 향상시킬 수 있다.

- [0041] 이러한 활성층(4)은 상기 n형 질화물 반도체층(3)과 같이 유기금속 기상증착법, 분자빔 성장법 또는 하이브리드 기상증착법과 같은 공지의 증착공정을 사용하여 상기 n형 질화물 반도체층(3) 상에 형성될 수 있다.

- [0042] p형 질화물 반도체충(5)은 n형 질화물 반도체충(3)과 마찬가지로, p형 도펀트로 도핑된 반도체 물질로 이루어질 수 있으며, 대표적인 질화물 반도체 물질로는 GaN, AlGaN, InGaN가 있다. p형 질화물 반도체충(5)의 도핑에 사용되는 도펀트로는 Mg, Zn 또는 Be 등이 있으며, 이중 Mg가 대표적으로 사용된다.

- [0043] 이러한 p형 질화물 반도체층(5)은, 상기 반도체 물질을 유기금속 기상증착법, 분자빔 성장법 또는 하이브리드 기상증착법과 같은 공지의 증착공정을 사용하여 상기 활성층(4) 상에 성장시킴으로써 형성된다.

- [0044] 전국(6, 7)은 p형 질화물 반도체충(5)의 상면에 형성되는 p측 본딩전국(6)과, n형 질화물 반도체충(3)의 상면에 형성되는 n측 본딩전국(7)을 포함한다.

- [0045] 또한, p형 질화물 반도체층(5)과 p측 본당전극(6) 사이에, p형 질화물 반도체층(5)의 상면의 전 영역에 형성되는 투명전극층을 더 구비할 수 있다. 투명전극층은 비교적 높은 에너지 밴드갭을 갖는 p형 질화물 반도체층(5)과의 접촉저항을 낮추는데 적절하면서, 동시에 활성층(4)에서 생성되는 광이 상부로 방출되기 위해 양호한 투광

성을 갖는 물질로 형성될 것이 요구된다. 일반적으로 투명전극층은 투광성을 확보하기 위해 산화인듐주석(ITO), 산화카드뮴주석(CTO) 또는 질화티탄텅스텐(TiWN)으로 재료로 사용할 수 있다. 이러한 투명전극층은 화학기상증 착법(Chemical Vapor Deposition : CVD) 및 전자빔 증발법(E-beam evaporator)과 같은 공지의 증착방법 또는 스퍼터링(sputtering) 등의 공정에 의해 형성될 수 있으며, 오믹콘택의 특성을 향상시키기 위해서 약 400℃ 내지 900℃의 온도에서 열처리될 수 있다.

- [0046] p측 본딩전극(6)은 p형 질화물 반도체충(5) 상에 형성된다. 상기 p측 본딩전극(6)은 와이어 본딩을 통해 리드 상에 탑재될 최외곽 전극층으로서, 일반적으로 Au 또는 Au를 함유한 합금을 재료로 하여 화학기상증착법 및 전 자빔 증발법과 같은 공지의 증착방법 또는 스퍼터링 등의 공정에 의해 형성될 수 있다.

- [0047] n측 본딩전극(7)은 n형 질화물 반도체층(3) 상에 Ti, Cr, Al, Cu 및 Au로 구성된 그룹으로부터 선택된 물질로 이루어진 단일층 또는 복수층으로 형성될 수 있다. 이러한 n측 본딩전극(7)은 화학기상증착법 및 전자빔 증발법과 같은 공지의 증착방법 또는 스퍼터링 등의 공정에 의해 n형 질화물 반도체층(3) 상에 형성될 수 있다.

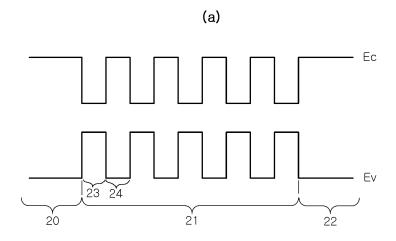

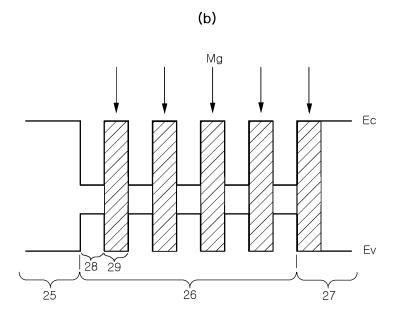

- [0048] 도 2는 도 1에 도시된 본 발명의 한 실시 형태인 질화물 반도체 발광소자의 활성층에 있어서, 장벽층(24)에 Mg 도핑을 할 경우에 따른 밴드(band) 구조의 변화를 모식적으로 나타낸 도면이다.

- [0049] 도 2의 (a)는 n형 질화물 반도체층(20)과 p형 질화물 반도체층(22) 사이에 형성된 활성층(21)의 장벽층(24)에 Mg를 도핑하지 않았을 때의 밴드갭 모식도이며, 도 2의 (b)는 장벽층(29)에 Mg를 도핑한 경우의 밴드갭 모식도이다.

- [0050] 도 2의 (b)에 도시된 바와 같이, 활성층(26)의 다중 양자 우물 구조는 p형 도펀트인 Mg가 도프된 장벽층(29)과 언도프된 우물층(28)이 순차적으로 적층된 구조를 가지며, 장벽층(29)의 Mg 도핑은 장벽층 전체에 수행되거나 일부 장벽층에만 수행될 수 있으며, 적어도 p형 질화물 반도체층(27)과 가장 인접한 장벽층에는 Mg 도핑을 수행한다.

- [0051] 즉, 일부 장벽층에만 Mg 도핑을 하는 경우에도 해당 우물층으로의 정공 주입 효율을 높일 수 있다. 상기 p형 도 펀트는 Mg, Zn, Be, Ca, Sr 및 Ba 중 하나일 수 있으며, Mg가 바람직하다. p형 도펀트의 도핑 농도는  $10^{15}$ /cm²  $\sim 10^{20}$ /cm² 인 것이 바람직하다.

- [0052] 구체적으로, n형 질화물 반도체층(25)과 p형 질화물 반도체층(27) 사이에 형성된 활성층(26)의 장벽층(29)에 Mg 도핑을 실시하게 되면, 전도대에 대한 우물층(28)의 깊이가 깊어져 이동도가 높은 전자를 우물층에 구속하는 효과를 높일 수 있고, 상대적으로 정공에 대하여는 가전자대의 우물층(28) 깊이가 낮아져서 주입 효율을 높일 수 있다.

- [0053] 이러한 활성층의 장벽층(29)에 도핑된 Mg 확산을 방지하기 위하여 장벽층의 Mg 도핑된 p형 도핑 장벽층 전후로 언도프된 장벽층을 성장시킬 수 있다. 예를 들어, 장벽층에 p형 도펀트가 도핑될 때, Mg 도핑된 p형 도핑 장벽층 및 언도프된 장벽층이 순차 적층된 구조, 또는 언도프된 장벽층 및 Mg 도핑된 p형 도핑 장벽층이 순차 적층된 구조, 또는 언도프된 장벽층이 순차 적층된 구조 중 적어도 하나의 구조를 가질 수 있다. 상술한 활성층의 구조에 대해서는 도 3 내지 도 4에서 상세히 설명한다.

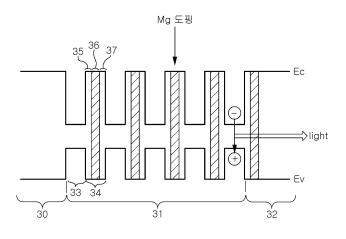

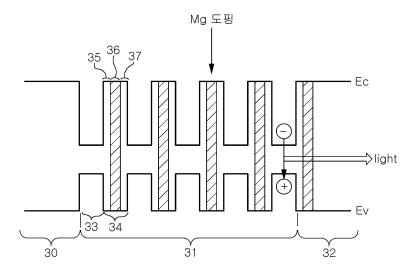

- [0054] 도 3은 도 1에 도시된 본 발명의 한 실시의 형태인 질화물 반도체 발광소자의 활성층의 양자 우물 밴드(band) 구조를 모식적으로 나타낸 도면이다.

- [0055] 도 3에 도시된 바와 같이, 다중 양자 우물 구조를 가지는 활성층(31)에서 장벽층(34)을 Mg 도핑을 통하여 p형 도핑 장벽층(36)으로 만들어 줌으로써, 정공의 낮은 이동도에 의해 p형 질화물 반도체층(32)에서 효과적으로 활성층(31)으로 주입되지 못하는 정공을 장벽층(34)에서 우물층(33)으로 바로 주입시킨다. 이렇게 함으로써 질화물 반도체 발공소자의 발광효율을 현저하게 개선 시키고, 또한 전자가 p형 질화물 반도체층(32)으로 오버플로우 (overflow) 되는 것을 방지할 수 있다.

- [0056] 한편, 일반적인 LED에서는 전자의 빠른 이동도로 인하여 p형 질화물 반도체층(32)에 가장 가까운 영역의 우물층에서만 발광이 일어나게 되는데, 장벽층(34)을 p형 도핑 장벽층(36)으로 만들게 되면 발광되는 우물층의 숫자 또한 늘릴 수 있게 된다. 하지만 장벽층(34)에 도핑된 Mg의 경우, 활성층 이후에 성장되는 p형 질화물 반도체층의 성장 온도가 높아서 우물층 내부로의 확산이 일어날 수 있으며, 이러한 경우 Mg가 결함(defect)으로 작용하여 발광 효율을 떨어뜨리게 된다.

- [0057] 따라서 본 발명에서는, 활성층(31)에 있어서, 장벽층(34)의 Mg 도핑된 p형 도핑 장벽층(36) 전후로 언도프된 장

벽층(35, 37)을 성장시켜 우물층(33)으로의 Mg 확산을 방지한다. 이에 의해 Mg 확산에 따른 발광 효율의 저하를 방지한다.

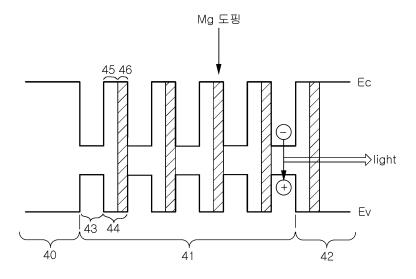

- [0058] 도 4는 본 발명의 다른 한 실시 형태에 따른 활성충의 양자 우물 밴드(band) 구조를 모식적으로 나타낸 도면이다.

- [0059] 도 4에 도시된 바와 같이, 본 발명의 활성층(41)에 있어서, 장벽층(44)에 도핑된 Mg의 우물층(44)으로의 확산을 방지하기 위해, 장벽층(44)의 Mg 도핑된 p형 도핑 장벽층(45)의 일측에 언도프된 장벽층(44)을 성장시킬 수 있다. 이러한 구조에 의해서도, 도 3의 경우와 같이, Mg 확산에 따른 발광 효율의 저하를 방지할 수 있다.

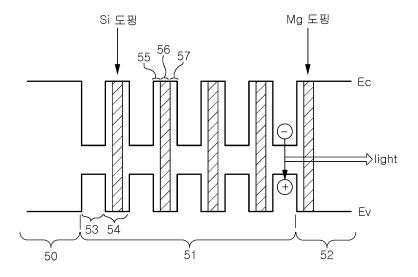

- [0060] 도 5는 본 발명의 또 다른 한 실시 형태의 질화물 반도체 발광소자의 활성층의 장벽층에 Si 및 Mg를 도핑할 경우에 따른 밴드(band) 구조의 변화를 모식적으로 나타낸 도면이다.

- [0061] 일반적인 비발광 결합의 원인은 캐리어 농도에 의하여 생기는 비발광 오제(Auger) 결합과, 결함(defect)에 의하여 생기는 밴드갭 내의 딥 레벨(deep level)에 의한 비발광 결합인 쇼클리-리드-홀(shockley-read-hall) 결합이었으며, 쇼클리-리드-홀(shockley-read-hall) 결합의 결합률은 캐리어 농도에 비례하지만, 비발광 오제(Auger) 결합의 경우 결합률이 캐리어 농도의 세제곱에 비례한다.

- [0062] 따라서 고전류 밀도에 따른 활성층 내부에서 캐리어 농도가 높아질수록 캐리어 농도의 세제곱에 비례하는 비발 광 오제(Auger) 결합이 일어날 확률이 높아지게 되며, 이것에 의하여 고전류 밀도에서 외부 양자 효율이 감소하게 된다.

- [0063] Si 도핑에 의해 장벽층에서의 캐리어 농도가 높아질수록 우물층에서의 캐리어와 상호작용을 통하여 장벽층의 전자가 비발광 오제(Auger) 결합에 참여할 수 있는 확률이 높아지게 된다. 또한, 도핑을 하지 않은 장벽층의 경우에도 일반적으로 언도프된 GaN의 경우 막질이 아주 우수할 때,  $10^{16}/\mathrm{cm}^{2}$  정도의 전자 농도를 가진다. 이는 질소공간(Nitrogen vacancy)에 의하여 발생하는 것으로서 GaN의 물질 특성이다.

- [0064] 위와 같은  $10^{16}$ /cm 정도의 전자 농도는 버퍼층 위에 성장되는 언도프된 GaN층의 성장 조건에 해당하는 것으로서, 성장 조건이 다른 활성층 내의 장벽층 성장시에는  $10^{16}$ /cm 와 비슷하거나 혹은 그 이상의 전자 농도를 가질 것으로 예상된다. 이러한 경우 역시 장벽층의 전자가 비발광 오제(Auger) 결합에 참여할 가능성이 생기게 된다.

- [0065] 따라서 본 발명에서는 도 5에 도시된 바와 같이, 활성층(51)에서 주로 빛이 발광하게 되는 p형 질화물 반도체층 (52)에 인접한 장벽층, 즉 마지막 우물층 또는 일부 장벽층에 Mg 도핑을 하고, n형 질화물 반도체층(50)에 인접한 장벽층(54) 또는 일부 장벽층에 Si 도핑을 수행한다.

- [0066] 이렇게 함으로써 장벽층(54)이 인슐레이터(insulator)가 됨으로써 생길 수 있는 발광소자의 동작 전압의 증가를 감소시킬 수 있다. 이때, n형 도펀트은 Si뿐만 아니라, Ge, Se, Te 및 C 중 하나일 수 있으며, p형 도펀트는 Mg 뿐만 아니라, Zn, Be, Ca, Sr 및 Ba 중 하나일 수 있다.

- [0067] 그리고, n형 도펀트의 도핑 농도는  $10^{15}/cm^2 \sim 10^{20}/cm^2$  이며, p형 도펀트의 도핑 농도는  $10^{15}/cm^2 \sim 10^{20}/cm^2$  인 것이 바람직하다.

- [0068] 그리고, 장벽층(54)의 Si 또는 Mg 도핑된 도핑 장벽층(56)의 전후로 언도프된 장벽층(55, 57)을 성장시키거나 장벽층(54)의 Si 또는 Mg 도핑된 도핑 장벽층(56)의 일측에만 언도프된 장벽층(55 또는 57)을 성장시킬 수 있다.

- [0069] 이와 같이 장벽층에 Mg 도핑을 통하여 인슐레이터(insulator)에 가까운 특성을 얻게 되면, 장벽층에서 캐리어의 농도가  $10^{15}/cm$  이하로 매우 낮아지게 되므로 장벽층의 캐리어가 비발광 오제 결합에 참여할 수 있는 기회를 현저하게 낮출 수 있고, 이렇게 하여 고전류에서도 비발광 오제 결합을 감소시켜 높은 양자 효율을 얻을 수 있다. 이러한 경우는 도 2 내지 도 4의 경우보다 작은 농도의 Mg 도핑을 행해야 한다.

- [0070] 이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만, 본 발명의 권리 범위는 이에 한정되는 것은 아니고 첨부된 청구범위에 기재된 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 다양한 형태의 치환, 변형 및 변경이 가능하다는 것은 당 기술 분야의 통상의 지식을 가진 자에게 자명할 것이다.

- [0071]

# 도면의 간단한 설명

- [0072] 도 1은 본 발명의 바람직한 한 실시 형태인 질화물 반도체 발광소자의 구조를 나타낸 단면도,

- [0073] 도 2는 본 발명의 바람직한 한 실시 형태인 질화물 반도체 발광소자의 활성층의 장벽층에 Mg 도핑을 할 경우에 따른 밴드(band) 구조의 변화를 모식적으로 나타낸 도면으로, 도 2의 (a)는 장벽층에 Mg를 도핑하지 않았을 경우, 도 2의 (b)는 장벽층에 Mg를 도핑한 경우의 밴드갭 모식도,

- [0074] 도 3은 도 1에 따른 질화물 반도체 발광소자의 활성층의 양자 우물 밴드(band) 구조를 모식적으로 나타낸 도면,

- [0075] 도 4는 본 발명의 다른 한 실시 형태에 따른 활성층의 양자 우물 밴드(band) 구조를 모식적으로 나타낸 도면, 그리고,

- [0076] 도 5는 본 발명의 또 다른 한 실시 형태의 질화물 반도체 발광소자의 활성층에 있어서, 장벽층에 Si 및 Mg를 도 핑할 경우에 따른 밴드(band) 구조의 변화를 모식적으로 나타낸 도면이다.

- [0077] <도면의 주요 부호에 대한 설명>

- [0078] 1. 기판

- 2. 버퍼층

- [0079] 3. n형 질화물 반도체층

- 4. 활성층

- [0080] 5. p형 질화물 반도체층

- 6. p측본딩전극

- [0081] 7. n측본딩전극

# 도면

# 도면1

# 도면2

# 도면3

# 도면4

# *도면5*